How can we understand the new logic of packaging in the age of the AI wave? — MST’s CTO is set to deliver an in-depth analysis!

On September 18, the 4th Innovation Summit Forum on Power Semiconductors and Advanced Packaging & Testing will be held in Wuxi. As a key platform for exchange in the fields of power semiconductors and advanced packaging, this forum will focus on cutting-edge packaging technologies, testing processes, and industrialization challenges, drawing together core companies, research institutions, and technical experts from across the upstream and downstream segments of the industry chain.

To better facilitate mutual exchange and collaboration in the fields of power semiconductors and advanced packaging & testing, Semiconductor Online will organize the 4th Power Semiconductor and Advanced Packaging & Testing Innovation Summit Forum on September 18, 2025, in Wuxi City. The event aims to provide a high-quality platform for collaborative innovation, driving academic research, technological advancements, and industrial growth in China’s power semiconductor and advanced packaging & testing sectors.

MST’s Chief Technology Officer and Co-founder, Wang Xin, will serve as an invited guest, delivering a keynote speech titled "Technical Features and Process Challenges of Hybrid Packaging."

Hybrid Packaging: Chip Design Enters the "Collaborative Era"

NEW TIME

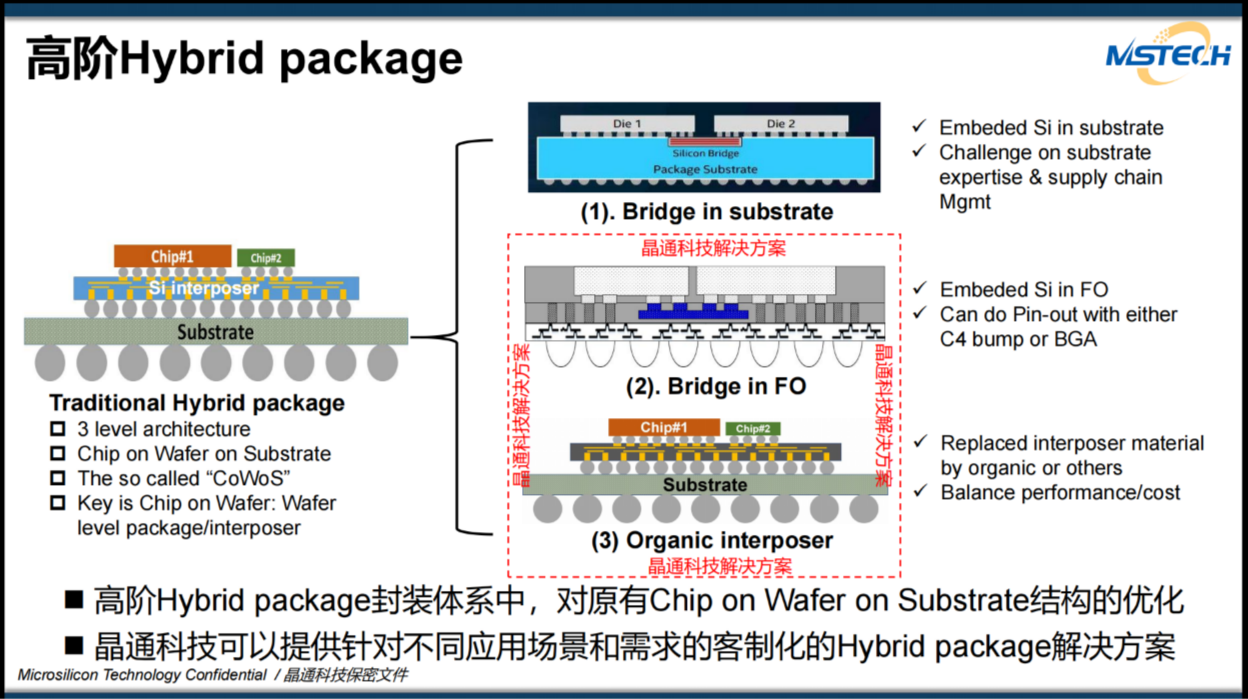

Currently, the rapid growth of applications such as artificial intelligence, large-scale models, and high-performance computing is driving the accelerated adoption of the Chiplet (chiplet-based) design approach in chip development. Under this model, efficiently and cost-effectively achieving 2.5D/3D integration has become a common challenge facing the industry.

Wang Xin will focus on sharing his insights and practical experience regarding the Hybrid Package at the upcoming forum.

01. Trends

HPC/SoC chips are increasingly adopting the Chiplet model, with hybrid packaging emerging as the most promising implementation approach.

02. Challenge

The technological integration of fan-out and interposer still faces bottlenecks in terms of yield, cost, and reliability.

03. Solution

MST has introduced an embedded silicon bridge fan-out hybrid packaging solution that demonstrates differentiated advantages in architectural design, interconnect performance, and process flow.

Wang Xin believes: "Future advanced packaging must break through process barriers and move toward multi-dimensional collaboration across design, architecture, materials, and equipment. Hybrid packaging is not merely a choice of technological roadmap—it is, in fact, the key to a system's competitive edge."

Forum Preview: Voices Worth Watching

PROSPECT

In the context where advanced packaging is increasingly becoming the semiconductor industry's "second battlefield," this forum's discussions will not only cover the iterative advancements in power semiconductors and testing processes, but will also focus on how system-level innovations can be effectively implemented. Wang Xin's presentation will provide upstream and downstream enterprises in the industry with a practical case study and valuable insights for consideration.

• How to understand the new packaging logic under the Chiplet wave?

• Can hybrid packaging be the optimal solution for balancing performance and cost?

• MST's advanced packaging solutions for AI chips

The answer will be revealed at the forum venue on September 18.

Speech Time: Thursday, September 18, 2025 Venue: Wuxi Suning Galaxy International Hotel, No. 109 Renmin Middle Road, Liangxi District, Wuxi City.

Tags:

Real-time Blog